## Final Report EASA\_REP\_RESEA\_2008\_1

**Research Project:**

Safety Implications of the use of systemon-chip (SoC) on commercial of-the-shelf (COTS) devices in airborne critical applications

#### **Disclaimer**

This study has been carried out for the European Aviation Safety Agency by an external organization and expresses the opinion of the organization undertaking the study. It is provided for information purposes only and the views expressed in the study have not been adopted, endorsed or in any way approved by the European Aviation Safety Agency. Consequently it should not be relied upon as a statement, as any form of warranty, representation, undertaking, contractual, or other commitment binding in law upon the European Aviation Safety Agency.

Ownership of all copyright and other intellectual property rights in this material including any documentation, data and technical information, remains vested to the European Aviation Safety Agency. All logo, copyrights, trademarks, and registered trademarks that may be contained within are the property of their respective owners.

Reproduction of this study, in whole or in part, is permitted under the condition that the full body of this Disclaimer remains clearly and visibly affixed at all times with such reproduced part.

# SOC SURVEY REPORT

# **EUROPEAN AVIATION SAFETY AGENCY**

<u>Authors:</u> Frédéric FAUBLADIER David RAMBAUD

### TABLE OF CONTENT

| 2. DEFINITION - COMPLEX DIGITAL COMPONENT.         26           2.1         COMPLEXITY CONSIDERATION.         26           2.2         COTS FAMILY.         26           2.2.1         Definition         26           2.2.2         Main Complex COTS         27           2.3         CUSTOM DEVICES         27           2.4         INTELLECTUAL PROPERTY CORE         28           2.5         SOC         29           3.         SOC SELECTION FOR THE SURVEY         32           3.1.1         Rational for selection         32           3.1.2         Freescale MPC 8641 D features         34           3.1.3         Texas Instrument: TMS320C6415T feature         36           3.2.1         Rational for selection         37           3.2.1         Rational for selection         37           3.2.2         Hardware micro-processor IP         38           3.2.3         Firmware micro-processor IP         38           3.3         SELECTION SUMMARY         39           3.3         SELECTION SUMMARY         39           3.3         SELECTION SUMMARY         39           3.4         YEUED DATA ASSESSMENT RESULT         40           4.1.1         S                                                                                   | 1. | INTRODU  | JCTION                                                           | 25 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|------------------------------------------------------------------|----|

| 2.2       COTS FAMILY       26         2.2.1       Definition       26         2.2.2       Main Complex COTS       27         2.3       CUSTOM DEVICES       27         2.4       INTELLECTUAL PROPERTY CORE       28         2.5       SoC       29         3. SOC SELECTION FOR THE SURVEY       32         3.1       Rational for selection       32         3.1.1       Rational for selection       32         3.1.2       Freescale MPC 8641 D features       34         3.1.3       Texas Instrument: TMS320C641ST feature       36         3.2       SOPC / IP       37         3.2.1       Rational for selection       37         3.2.2       Hardware micro-processor IP       38         3.2.3       Firmware micro-processor IP       38         3.2.4       Sothware micro-processor IP       38         3.3       SELECTION SUMMARY.       39         3.4       PUBLIC DATA ASSESMENT RESULT       40         4.1.1       Sothyare micro-processidentification and features determination.       40         4.1.1.2       Internal accessibility assessment.       40         4.1.1.3       User guides and Errata data assessment.       41     <                                                                                                         | 2. | DEFINITI | ON - COMPLEX DIGITAL COMPONENT                                   | 26 |

| 2.2.1       Definition       26         2.2.2       Main Complex COTS       27         2.3       CUSTOM DEVICES       27         2.4       INTELLECTUAL PROPERTY CORE       28         2.5       SOC       29         3.1       MICROPROCESSOR - SOC       32         3.1.1       Rational for selection       32         3.1.2       Freescale MPC 8641 D features       34         3.1.3       Texas Instrument: TMS320C6415T feature       36         3.2.2       SOPC/IP       37         3.2.1       Rational for selection       37         3.2.2       Hardware micro-processor IP       38         3.2.3       Firmware micro-processor IP       38         3.2.4       Software micro-processor IP       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY       39         3.4       PUBLIC DATA ASSESSMENT RESULT       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1       Step 1 - On chip cores identification and features assessment       42         4.1.1.3       User guides and Errata data assessment       42         4.1.1.4       Silicon                                                                                                    |    | 2.1 COM  | IPLEXITY CONSIDERATION                                           |    |

| 2.2.1       Definition       26         2.2.2       Main Complex COTS       27         2.3       CUSTOM DEVICES       27         2.4       INTELLECTUAL PROPERTY CORE       28         2.5       SOC       29         3.1       MICROPROCESSOR - SOC       32         3.1.1       Rational for selection       32         3.1.2       Freescale MPC 8641 D features       34         3.1.3       Texas Instrument: TMS320C6415T feature       36         3.2.2       SOPC/IP       37         3.2.1       Rational for selection       37         3.2.2       Hardware micro-processor IP       38         3.2.3       Firmware micro-processor IP       38         3.2.4       Software micro-processor IP       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY       39         3.4       PUBLIC DATA ASSESSMENT RESULT       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1       Step 1 - On chip cores identification and features assessment       42         4.1.1.3       User guides and Errata data assessment       42         4.1.1.4       Silicon                                                                                                    |    | 2.2 COT  | S FAMILY                                                         |    |

| 2.2.2       Main Complex COTS       27         2.3       Custom Devices       27         2.4       INTELLECTUAL PROFERTY CORE       28         2.5       SOC       29         3.       SOC SELECTION FOR THE SURVEY       32         3.1       MICROPROCESSOR – SOC       32         3.1.1       Rational for selection       32         3.1.2       Freescale MPC 8641 D features       34         3.1.3       Texas Instrument: TMS320C641ST feature       36         3.2       SOPC /IP       37         3.2.1       Rational for selection       37         3.2.2       Hardware micro-processor IP       38         3.2.3       Firmware micro-processor IP       38         3.2.4       Software micro-processor IP       38         3.3       SELECTION SUMMARY       39         3.3       SELECTION SUMMARY       39         3.4       Software micro-processor IP       38         3.5       Development tools       39         3.6       SELECTION SUMMARY       39         3.7       SELECTION SUMMARY       39         3.8       SELECTION SUMMARY       39         3.4       PUBLIC DATA ASSESSMENT RESULT <td></td> <td></td> <td></td> <td></td>                                                                                                           |    |          |                                                                  |    |

| 2.3       CUSTOM DEVICES       27         2.4       INTELLECTUAL PROPERTY CORE       28         2.5       SoC       29         3.       SOC SELECTION FOR THE SURVEY       32         3.1       MICROPROCESSOR - SoC.       32         3.1.1       Rational for selection.       32         3.1.2       Freescale MPC 8641 D features.       34         3.1.3       Texas Instrument: TMS320C6415T feature       36         3.2       SOPC / IP.       37         3.2.1       Rational for selection.       37         3.2.2       Hardware micro-processor IP.       38         3.2.3       Firmware micro-processor IP.       38         3.2.4       Software micro-processor IP.       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY.       39         4.1       SOPC / IP.       40         4.1.1       Step 1 - On chip cores identification and features determination.       40         4.1.1.1       Features assessment - activation/deactivation       40         4.1.1.3       User guides and Errata data assessment.       43         4.1.1.4       Silicon errata       43         4.1.1.5       Step 1 - Conclu                                                                                                    |    |          |                                                                  |    |

| 2.5       SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |          |                                                                  |    |

| 2.5       SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |          |                                                                  |    |

| 3.1       MICROPROCESSOR - SoC       32         3.1.1       Rational for selection.       32         3.1.2       Freescale MPC 8641 D features.       34         3.1.3       Texas Instrument: TMS320C6415T feature.       36         3.2       SOPC / IP       37         3.2.1       Rational for selection.       37         3.2.2       Hardware micro-processor IP       38         3.2.3       Firmware micro-processor IP       38         3.2.4       Software micro-processor IP       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY       39         4.       PUBLIC DATA ASSESSMENT RESULT       40         4.1.1       Step 1 - On chip cores identification and features determination.       40         4.1.1       Step 1 - On chip cores identification and features determination.       40         4.1.1.1       User guides and Errata data assessment.       42         4.1.1.3       User guides and Errata data assessment.       43         4.1.2       Step 1 - Fault tolerance and fail safe features assessment.       44         4.1.2.1       Failure modes assessment.       44         4.1.2.2       Herrata data transfers failure.       47 <td< td=""><td></td><td></td><td></td><td></td></td<> |    |          |                                                                  |    |

| 3.1.1       Rational for selection.       32         3.1.2       Freescale MPC 8641 D features.       34         3.1.3       Texas Instrument: TMS320C6415T feature.       36         3.2       SoPC/IP.       37         3.2.1       Rational for selection.       37         3.2.2       Hardware micro-processor IP.       38         3.2.3       Firmware micro-processor IP.       38         3.2.4       Software micro-processor IP.       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY.       39         3.4       PUBLIC DATA ASSESSMENT RESULT       40         4.1       SoPC/IP.       40         4.1.1       Step 1 - On chip cores identification and features determination.       40         4.1.1       Step 1 - On chip cores identification and features determination.       40         4.1.1.1       Features assessment       42         4.1.1.3       User guides and Errata data assessment.       42         4.1.1.4       Silicon errata.       43         4.1.2       Step 1 - conclusion.       43         4.1.2.3       Internal data transfers failure       44         4.1.2.4       Unused functions deactivation failure                                                                        | 3. | SOC SEL  | ECTION FOR THE SURVEY                                            | 32 |

| 3.1.2       Freescale MPC 8641 D features       34         3.1.3       Texas Instrument: TMS320C6415T feature       36         3.2       SoPC/IP       37         3.2.1       Rational for selection       37         3.2.2       Hardware micro-processor IP       38         3.2.3       Firmware micro-processor IP       38         3.2.4       Software micro-processor IP       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY       39         4.       PUBLIC DATA ASSESSMENT RESULT       40         4.1       SoPC / IP       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1.2       Internal accessibility assessment       41         4.1.1.4       Silicon errata       43         4.1.1.5       Step 1 - conclusion       43         4.1.1.4       Silicon errata       43         4.1.1.5       Step 1 - conclusion       43         4.1.2.1       Faiure modes assessment       44 <td></td> <td>3.1 Mici</td> <td>ROPROCESSOR – SoC</td> <td></td>    |    | 3.1 Mici | ROPROCESSOR – SoC                                                |    |

| 3.1.2       Freescale MPC 8641 D features       34         3.1.3       Texas Instrument: TMS320C6415T feature       36         3.2       SoPC/IP       37         3.2.1       Rational for selection       37         3.2.2       Hardware micro-processor IP       38         3.2.3       Firmware micro-processor IP       38         3.2.4       Software micro-processor IP       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY       39         4.       PUBLIC DATA ASSESSMENT RESULT       40         4.1       SoPC / IP       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1.2       Internal accessibility assessment       41         4.1.1.4       Silicon errata       43         4.1.1.5       Step 1 - conclusion       43         4.1.1.4       Silicon errata       43         4.1.1.5       Step 1 - conclusion       43         4.1.2.1       Faiure modes assessment       44 <td></td> <td>311</td> <td>Rational for selection</td> <td>32</td>  |    | 311      | Rational for selection                                           | 32 |

| 3.1.3       Texas Instrument: TMS320C6415T feature       36         3.2       SOPC/IP       37         3.2.1       Rational for selection       37         3.2.2       Hardware micro-processor IP       38         3.2.3       Firmware micro-processor IP       38         3.2.4       Software micro-processor IP       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY       39         4.       PUBLIC DATA ASSESSMENT RESULT       40         4.1       SOPC/IP       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1       Features assessment – activation/deactivation       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1.2       Internal accessibility assessment       42         4.1.1.3       User guides and Errata data assessment       43         4.1.1.4       Slicon errata       43         4.1.2       Step 2 - Fault tolerance and fail safe features assessment       44         4.1.2.1       Failure modes assessment       44         4.1.2.2       Memory upsets       47         4.1.2.3       Internal data t                                                        |    | -        |                                                                  |    |

| 3.2       SOPC / IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | ••••     |                                                                  |    |

| 3.2.2       Hardware micro-processor IP       38         3.2.3       Firmware micro-processor IP       38         3.2.4       Software micro-processor IP       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY       39         3.4       PUBLIC DATA ASSESSMENT RESULT       40         4.1       SoPC / IP       40         4.1.1       Features assessment – activation/deactivation       40         4.1.2       Internal accessibility assessment.       42         4.1.3       User guides and Errata data assessment.       43         4.1.4       Silicon errata.       43         4.1.5       Step 1 conclusion.       43         4.1.2       Memory upsets.       47         4.1.2.1       Failure modes assessment .       44         4.1.2.2       Memory upsets.       47         4.1.2.3       Internal data transfers failure       47<                                                                 |    |          |                                                                  |    |

| 3.2.2       Hardware micro-processor IP       38         3.2.3       Firmware micro-processor IP       38         3.2.4       Software micro-processor IP       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY       39         3.4       PUBLIC DATA ASSESSMENT RESULT       40         4.1       SoPC / IP       40         4.1.1       Features assessment – activation/deactivation       40         4.1.2       Internal accessibility assessment.       42         4.1.3       User guides and Errata data assessment.       43         4.1.4       Silicon errata.       43         4.1.5       Step 1 conclusion.       43         4.1.2       Memory upsets.       47         4.1.2.1       Failure modes assessment .       44         4.1.2.2       Memory upsets.       47         4.1.2.3       Internal data transfers failure       47<                                                                 |    | 3.2.1    | Rational for selection.                                          |    |

| 3.2.3       Firmware micro-processor IP       38         3.2.4       Software micro-processor IP       38         3.2.5       Development tools       39         3.3       SELECTION SUMMARY.       39         4. <b>PUBLIC DATA ASSESSMENT RESULT</b> 40         4.1       SoPC/IP       40         4.1.1       Step 1 - On chip cores identification and features determination.       40         4.1.1       Teatures assessment – activation/deactivation       40         4.1.1.2       Internal accessibility assessment.       42         4.1.1.3       User guides and Errata data assessment.       43         4.1.1.4       Silicon errata       43         4.1.2       Step 1 - conclusion.       43         4.1.2       Step 2 - Fault tolerance and fail safe features assessment.       44         4.1.2.1       Failure modes assessment.       44         4.1.2.2       Memory upsets.       47         4.1.2.4       Unused functions deactivation failure       47         4.1.2.5       Timeout failure       48         4.1.2.6       Microcode design errors.       48         4.1.3       Step 3 - Verification and design Tools assessment       48         4.1.3.1       Tools                                                                    |    | -        |                                                                  | -  |

| 3.2.4       Software micro-processor IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 3.2.3    |                                                                  |    |

| 3.3       SELECTION SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 3.2.4    |                                                                  |    |

| 4.       PUBLIC DATA ASSESSMENT RESULT       40         4.1       SoPC/IP       40         4.1.1       Step 1 - On chip cores identification and features determination       40         4.1.1       Features assessment – activation/deactivation       40         4.1.1.1       Features assessment – activation/deactivation       40         4.1.1.2       Internal accessibility assessment       42         4.1.1.3       User guides and Errata data assessment       43         4.1.1.4       Silicon errata       43         4.1.1.5       Step 1 conclusion       43         4.1.2       Step 1 conclusion       43         4.1.2.5       Step 1 conclusion       44         4.1.2.1       Failure modes assessment       44         4.1.2.2       Memory upsets       47         4.1.2.3       Internal data transfers failure       47         4.1.2.4       Unused functions deactivation failure       47         4.1.2.5       Timeout failure       48         4.1.2.6       Microcode design errors       48         4.1.3       Step 3 - Verification and design Tools assessment       48         4.1.3       Step 3 - conclusion       49         4.1.4       Step 4 - SoC qualification asses                                                        |    | 3.2.5    | Development tools                                                |    |

| 4.1       SOPC / IP       40         4.1.1       Step 1 - On chip cores identification and features determination.       40         4.1.1       Features assessment – activation/deactivation       40         4.1.1.1       Features assessment – activation/deactivation       40         4.1.1.2       Internal accessibility assessment.       42         4.1.1.3       User guides and Errata data assessment.       42         4.1.1.4       Silicon errata       43         4.1.1.5       Step 1 conclusion       43         4.1.1.5       Step 2 - Fault tolerance and fail safe features assessment       44         4.1.2.1       Failure modes assessment       44         4.1.2.2       Memory upsets.       47         4.1.2.3       Internal data transfers failure       47         4.1.2.4       Unused functions deactivation failure       47         4.1.2.5       Timeout failure       48         4.1.2.6       Microcode design errors       48         4.1.2.7       Step 3 - Verification and design Tools assessment       48         4.1.3       Tools       48         4.1.3.1       Tools       48         4.1.3.2       On chip debug facilities       49         4.1.4       Step 4                                                         |    | 3.3 Sele | ECTION SUMMARY                                                   |    |

| 4.1.1       Step 1 - On chip cores identification and features determination.       40         4.1.1       Features assessment – activation/deactivation       40         4.1.2       Internal accessibility assessment.       42         4.1.3       User guides and Errata data assessment.       43         4.1.4       Silicon errata       43         4.1.5       Step 1 conclusion       43         4.1.6       Step 2 - Fault tolerance and fail safe features assessment       44         4.1.2.1       Failure modes assessment       44         4.1.2.2       Memory upsets       47         4.1.2.3       Internal data transfers failure       47         4.1.2.4       Unused functions deactivation failure       48         4.1.2.5       Timeout failure       48         4.1.2.6       Microcode design errors       48         4.1.2.7       Step 2 conclusion       48         4.1.3       Step 3 - Verification and design Tools assessment       48         4.1.3       Tools       49         4.1.3.1       Tools       49         4.1.4       Step 4 - SoC qualification assessment       49         4.1.4       Track record of production       49         4.1.4.1       Track record of                                                         | 4. | PUBLIC I | DATA ASSESSMENT RESULT                                           | 40 |

| 4.1.1.1Features assessment – activation/deactivation404.1.1.2Internal accessibility assessment424.1.1.3User guides and Errata data assessment434.1.1.4Silicon errata434.1.1.5Step 1 conclusion434.1.2Step 2 - Fault tolerance and fail safe features assessment444.1.2.1Failure modes assessment444.1.2.2Memory upsets474.1.2.3Internal data transfers failure474.1.2.4Unused functions deactivation failure474.1.2.5Timeout failure484.1.2.6Microcode design errors484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 - Soc qualification assessment494.1.4Track record of production494.1.4.4Soc gualification504.1.4.4Soc service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 4.1 SoP  | С / IP                                                           | 40 |

| 4.1.1.1Features assessment – activation/deactivation404.1.1.2Internal accessibility assessment424.1.1.3User guides and Errata data assessment434.1.1.4Silicon errata434.1.1.5Step 1 conclusion434.1.2Step 2 - Fault tolerance and fail safe features assessment444.1.2.1Failure modes assessment444.1.2.2Memory upsets474.1.2.3Internal data transfers failure474.1.2.4Unused functions deactivation failure474.1.2.5Timeout failure484.1.2.6Microcode design errors484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 - Soc qualification assessment494.1.4Track record of production494.1.4.4Soc gualification504.1.4.4Soc service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 4.1.1    | Step 1 - On chip cores identification and features determination |    |

| 4.1.1.3User guides and Errata data assessment434.1.1.4Silicon errata434.1.1.5Step 1 conclusion434.1.2Step 2 - Fault tolerance and fail safe features assessment444.1.2.1Failure modes assessment444.1.2.2Memory upsets474.1.2.3Internal data transfers failure474.1.2.4Unused functions deactivation failure474.1.2.5Timeout failure484.1.2.6Microcode design errors484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 conclusion494.1.4Track record of production494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 4.1.1.1  |                                                                  |    |

| 4.1.1.4Silicon errata434.1.1.5Step 1 conclusion434.1.2Step 2 - Fault tolerance and fail safe features assessment444.1.2.1Failure modes assessment444.1.2.2Memory upsets474.1.2.3Internal data transfers failure474.1.2.4Unused functions deactivation failure474.1.2.5Timeout failure484.1.2.6Microcode design errors484.1.2.7Step 2 conclusion484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 4.1.1.2  |                                                                  |    |

| 4.1.1.5Step 1 conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 4.1.1.3  | 3 User guides and Errata data assessment                         | 43 |

| 4.1.2Step 2 - Fault tolerance and fail safe features assessment444.1.2.1Failure modes assessment444.1.2.2Memory upsets474.1.2.3Internal data transfers failure474.1.2.4Unused functions deactivation failure474.1.2.5Timeout failure484.1.2.6Microcode design errors484.1.2.7Step 2 conclusion484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |          | Silicon errata                                                   | 43 |

| 4.1.2.1Failure modes assessment444.1.2.2Memory upsets474.1.2.3Internal data transfers failure474.1.2.4Unused functions deactivation failure474.1.2.5Timeout failure484.1.2.6Microcode design errors484.1.2.7Step 2 conclusion484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 conclusion494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |          |                                                                  |    |

| 4.1.2.2Memory upsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |          |                                                                  |    |

| 4.1.2.3Internal data transfers failure474.1.2.4Unused functions deactivation failure474.1.2.5Timeout failure484.1.2.6Microcode design errors484.1.2.7Step 2 conclusion484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 conclusion494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |          |                                                                  |    |

| 4.1.2.4Unused functions deactivation failure474.1.2.5Timeout failure484.1.2.6Microcode design errors484.1.2.7Step 2 conclusion484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 conclusion494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |          |                                                                  |    |

| 4.1.2.5Timeout failure484.1.2.6Microcode design errors484.1.2.7Step 2 conclusion484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 conclusion494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |          |                                                                  |    |

| 4.1.2.6Microcode design errors.484.1.2.7Step 2 conclusion484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 conclusion494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |          |                                                                  |    |

| 4.1.2.7Step 2 conclusion484.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 conclusion494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |          |                                                                  |    |

| 4.1.3Step 3 - Verification and design Tools assessment484.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 conclusion494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |          |                                                                  |    |

| 4.1.3.1Tools484.1.3.2On chip debug facilities494.1.3.3Step 3 conclusion494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |          |                                                                  |    |

| 4.1.3.2On chip debug facilities494.1.3.3Step 3 conclusion494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | -        |                                                                  |    |

| 4.1.3.3Step 3 conclusion494.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | -        |                                                                  |    |

| 4.1.4Step 4 - SoC qualification assessment494.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |          |                                                                  |    |

| 4.1.4.1Track record of production494.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |          |                                                                  |    |

| 4.1.4.2Quality procedures504.1.4.3SoC qualification504.1.4.4SoC service experience50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |          |                                                                  |    |

| 4.1.4.3SoC qualification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 4.1.4.2  |                                                                  |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 4.1.4.3  |                                                                  |    |

| 4.1.4.5 Change process and problem reporting51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 4.1.4.4  |                                                                  |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 4.1.4.5  | 5 Change process and problem reporting                           | 51 |

|    | 4.1.4.6            | Obsolescence - guarantee - debug support                         | . 51 |

|----|--------------------|------------------------------------------------------------------|------|

|    | 4.1.4.7            | Step 4 conclusion                                                |      |

|    | 4.1.5 l            | Peripheral IP                                                    | . 51 |

|    | 4.1.5.1            | General overview                                                 |      |

|    | 4.1.5.2            | Safety impact assessment                                         |      |

|    |                    | SoPC conclusion                                                  |      |

|    |                    | AICROCONTROLLER                                                  |      |

|    | 4.2.1              | Step 1 - On chip cores identification and features determination | . 56 |

|    | 4.2.1.1            | Features assessment – activation/deactivation                    | . 56 |

|    | 4.2.1.2            | Internal accessibility assessment                                | . 59 |

|    | 4.2.1.3            | User guides and Errata data assessment                           | . 60 |

|    | 4.2.1.4            | Silicon errata                                                   | . 60 |

|    | 4.2.1.5            | Step 1 conclusion                                                | . 61 |

|    | 4.2.2              | Step 2 - Fault tolerance and fail safe features assessment       | . 62 |

|    | 4.2.2.1            | Failure modes assessment                                         |      |

|    | 4.2.2.2            | Memory upset protection                                          |      |

|    | 4.2.2.3            | Internal Data transfers failure                                  |      |

|    | 4.2.2.4            | Unused functions deactivation                                    |      |

|    | 4.2.2.5            | Timeout failure                                                  |      |

|    | 4.2.2.6            | Microcode design errors                                          |      |

|    | 4.2.2.7            | Step 2 conclusion                                                |      |

|    |                    | Step 3- Verification and design Tools assessment                 |      |

|    | 4.2.3.1            | Tools                                                            |      |

|    | 4.2.3.2            | On chip debug facilities                                         |      |

|    | 4.2.3.3            | Step 3 conclusion                                                |      |

|    |                    | Step 4 - SoC qualification assessment                            |      |

|    | 4.2.4.1            | Track record of production                                       |      |

|    | 4.2.4.2<br>4.2.4.3 | Quality procedures                                               |      |

|    | 4.2.4.3            | SoC qualification<br>SoC service experience                      |      |

|    | 4.2.4.4            | Change process and problem reporting                             |      |

|    | 4.2.4.6            | Obsolescence – guarantee – debug support                         |      |

|    | 4.2.4.7            | Step 4 conclusion                                                |      |

|    |                    | SoC microcontroller conclusion                                   |      |

| _  | -                  |                                                                  |      |

| 5. | PRIVATE            | DATA ASSESSMENT                                                  | 71   |

|    | 5.1 SoPC           | PROVIDER POSITION                                                | 71   |

|    | 5.2 SoC N          | AICROCONTROLLER POSITION                                         | 71   |

| ~  | DECOMM             |                                                                  | 70   |

| 6. |                    | ENDATIONS                                                        |      |

|    | 6.1 SOC N          | /ICROCONTROLLER RECOMMENDATIONS                                  | 72   |

|    | 6.1.1 l            | Introduction                                                     | 72   |

|    |                    | Approach overview                                                |      |

|    |                    | System development activities and SoC activities interaction     |      |

|    |                    | SoC microcontroller activities                                   |      |

|    |                    |                                                                  |      |

|    |                    | Verification consideration                                       |      |

|    |                    | Tools consideration                                              |      |

|    |                    | Configuration management consideration                           |      |

|    | 6.2.4              | SEU Management Consideration                                     | . 98 |

| 7. | CONCLUS            | ION                                                              | 99   |

|    |                    |                                                                  |      |

### LIST OF FIGURES

| FIGURE 1 – FROM THE PLD TO THE SOPC                                                | 30 |

|------------------------------------------------------------------------------------|----|

| FIGURE 2 – COTS AND CUSTOM DEVICES REPARTITION                                     |    |

| FIGURE 3 – CPU BOARDS ARCHITECTURE EVOLUTION                                       | 32 |

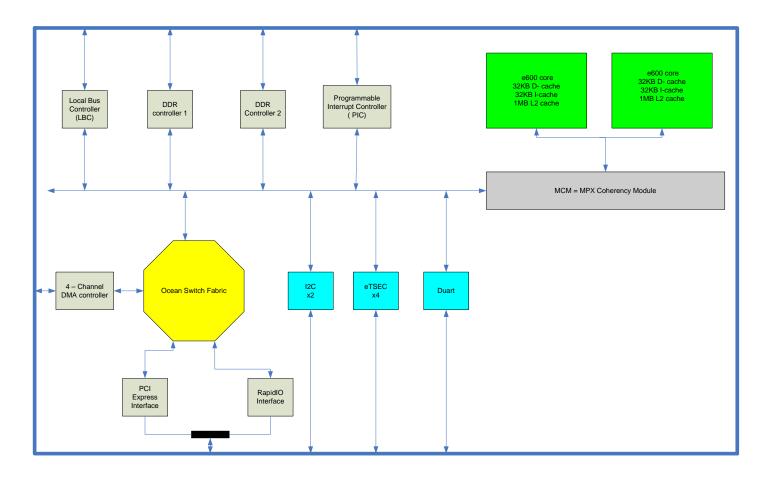

| FIGURE 4 – MPC8641D FUNCTIONAL OVERVIEW                                            | 34 |

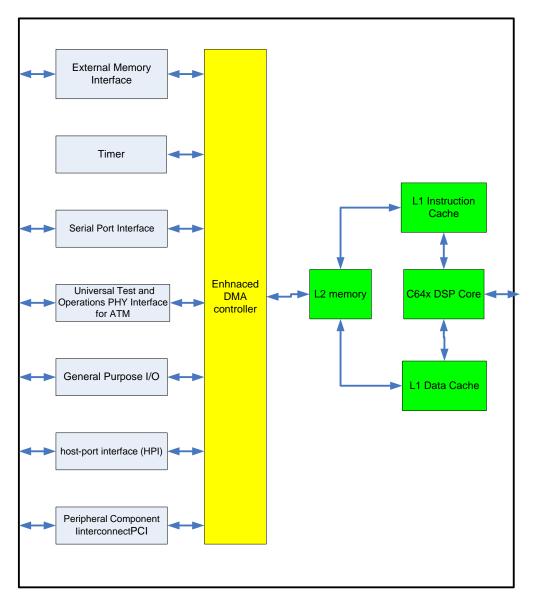

| FIGURE 5 – TMS320C6415T OVERVIEW                                                   | 36 |

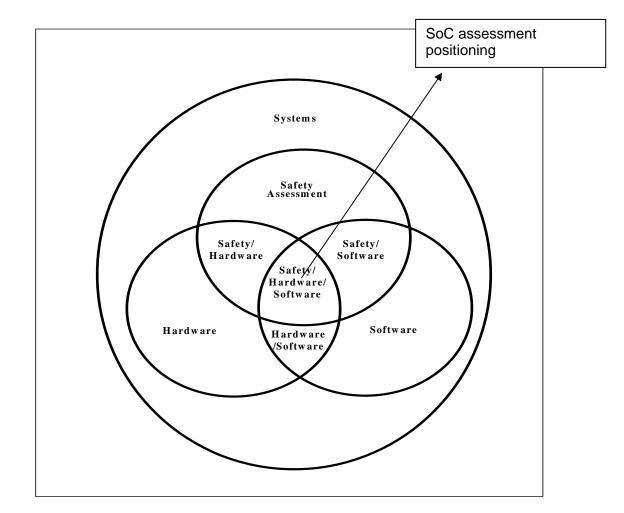

| FIGURE 6 - RELATIONSHIPS BETWEEN AIRBORNE SYSTEMS, SAFETY ASSESSMENT, HARDWARE AND |    |

| SOFTWARE PROCESSES                                                                 | 73 |

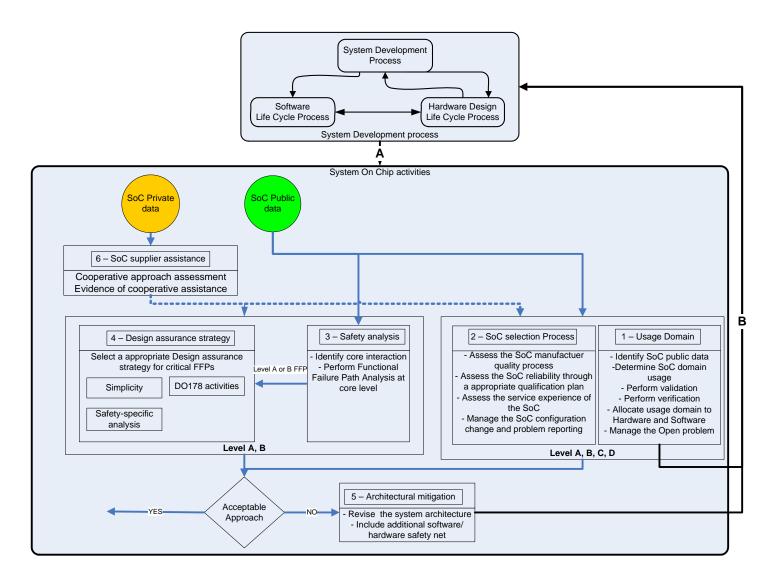

| FIGURE 7 – RECOMMENDATIONS FOR SOC MICROCONTROLLER USAGE                           | 74 |

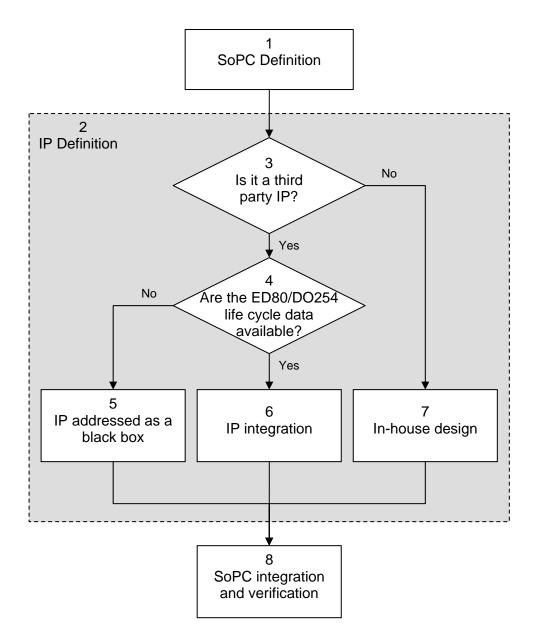

| FIGURE 8 – PROPOSED APPROACH FOR SOPC DESIGN                                       | 91 |

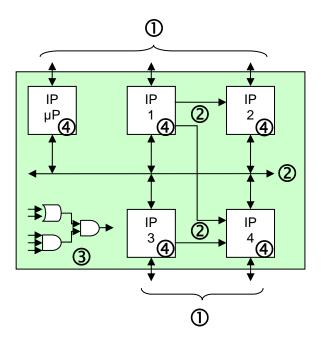

| FIGURE 9 – SOPC ARCHITECTURE DEFINITION DURING PHASE 1                             | 92 |

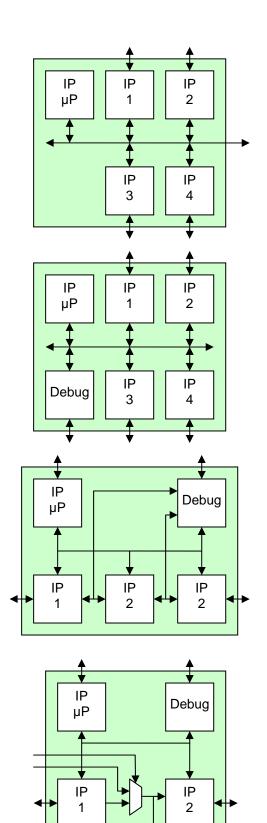

| FIGURE 10 – TESTABILITY ARCHITECTURE                                               | 97 |

### LIST OF TABLES

| TABLE 1 - STEP 1ASSESSMENT TOPICS                           | 19 |

|-------------------------------------------------------------|----|

| TABLE 2 - STEP 2 ASSESSMENT TOPICS                          | 21 |

| TABLE 3 - STEP 3 ASSESSMENT TOPICS                          |    |

| TABLE 4 - STEP 4 ASSESSMENT TOPICS                          | 23 |

| TABLE 5 - IP CATEGORIES                                     |    |

| TABLE 6 - SELECTION SUMMARY                                 |    |

| TABLE 7 - ACTIVITIES FOR SOC MICROCONTROLLER USE            |    |

| TABLE 8 - CONSTITUENTS TO DEFINE DURING THE SOPC DEFINITION | 93 |

|                                                             |    |

### LIST OF ACRONYMS

| μP    | Micro-processor                                  |

|-------|--------------------------------------------------|

| A/D   | Analog to Digital Converter                      |

| AHB   | Advanced High-performance Bus                    |

| ALU   | Arithmetic Logic Unit                            |

| APU   | Auxiliary Processor Unit                         |

| AQEC  | Aerospace Qualified Electronic Components        |

| ASIC  | Application Specific Integrated Circuit          |

| ATM   | Asynchronous Transfer Mode                       |

| ATMU  | Address Translation and Mapping Unit             |

| BHT   | Branch History Table                             |

| CAN   | Controller Area Network                          |

| CAT   | CATastrophic                                     |

| CEH   | Complex Electronic Hardware                      |

| CMA   | Common Mode Analysis                             |

| COTS  | Commercial Off-The-Shelf                         |

| CPLD  | Complex Programmable Logic Device                |

| CPU   | Central Processing Unit                          |

| CRC   | Cyclic Redundancy Check                          |

| CS    | Certification Specification                      |

| DDR   | Double Data Rate                                 |

| DER   | Designated Engineering Representatives           |

| DFS   | Dynamic Frequency Switching                      |

| DMA   | Direct Memory Access                             |

| DMSoC | Digital Media System-on-Chip                     |

| DPM   | Dynamic Power management                         |

| DSP   | Digital Signal Processor                         |

| DUART | Dual Universal Asynchronous Receiver Transmitter |

| EASA  | European Aviation Safety Agency                  |

| ECC   | Error Checking and Correcting                    |

| EDMA  | Enhanced Direct Memory Access                    |

| ESA   | European Space Agency                            |

| FAA   | Federal Aviation Administration                  |

| FAQ   | Frequently Asked Question                        |

|       | Eardenel Arde Cen. De sude Cene                  |

FAR

| FFP   | Functional Failure Path              |

|-------|--------------------------------------|

| FFPA  | Functional Failure Path Analysis     |

| FIFO  | First In First Out                   |

| FMEA  | Failure Mode Effect Analysis         |

| FPGA  | Field Programmable Grid Array        |

| FPU   | Floating Point Unit                  |

| FSL   | Fast Simplex Link                    |

| GAL   | General Array Logic                  |

| GPIO  | General Purpose Input/Output         |

| GPR   | Global Purpose Register              |

| GPL   | Global Public License                |

| HCI   | Hardware Configuration Index         |

| HDL   | Hardware Description Language        |

| HPI   | Host port interface                  |

| HSID  | Hardware Software Interface Document |

| HW    | HardWare                             |

| I2C   | Inter Integrated Circuit             |

| I/O   | Input / Output                       |

| IP    | Intellectual Property                |

| IPI   | Inter Processor Interrupt            |

| LAW   | Local Access Window                  |

| LBO   | Last Buy Order                       |

| LRM   | Line Replaceable Module              |

| LSU   | Load Store Unit                      |

| MB    | MicroBlaze                           |

| MBU   | Multiple Bit Upset                   |

| McBSP | Multichannel Buffered Serial Ports   |

| MCI   | Memory Controller Interface          |

| MCM   | MPX Coherency Module                 |

| MEU   | Multiple Event Upset                 |

| MMU   | Memory Management Unit               |

| MPX   | Multi Processor eXtension            |

| N/A   | Not Applicable                       |

| NDA   | Non Disclosure Agreement             |

| NVIC  | Nested Vector Interrupt Controller   |

| OCM   | On Chip Memory                       |

| OPB   | On chip Peripheral Bus               |

| OS     | Operating System                            |

|--------|---------------------------------------------|

| PAL    | Programmable Array Logic                    |

| PHAC   | Plan for Hardware Aspects of Certification  |

| PIC    | Programmable Interrupt Controller           |

| PCI    | Peripheral Component Interconnection        |

| PCle   | PCI Express                                 |

| PCN    | Product Change Notification                 |

| PLB    | Processor Local Bus                         |

| PLD    | Programmable Logic Device                   |

| PSSA   | Preliminary System Safety Assessment        |

| PWM    | Pulse Width Modulation                      |

| QOS    | Quality of Services                         |

| RISC   | Reduced Instruction Set Computer            |

| RTL    | Register Transfer Logic                     |

| SERDES | SERializator / DESserializator              |

| SEU    | Single Event Upset                          |

| SIMD   | Single Instruction Multiple Data            |

| SoC    | System on Chip                              |

| SoPC   | System on Programmable Chip                 |

| SRIO   | Serial Rapid Input Output                   |

| SRU    | Shop Replaceable Unit                       |

| SW     | SoftWare                                    |

| TCP    | Transmission Control Protocol               |

| TLB    | Translation Lookaside Buffer                |

| UART   | Universal Asynchronous Receiver Transmitter |

| UDP    | User Datagram Protocol                      |

| V&V    | Validation & Verification                   |

| VHDL   | Very high speed HDL                         |

| WCET   | Worst Case Execution Time                   |

|        |                                             |

### Acknowledgements

The authors wish to express their deep appreciation for the EASA assistance who have provided valuable comments and suggestions. The authors would also like to acknowledge their appreciation for the support of System on Chip providers (Freescale, Texas Instrument, Altera, Xilinx, Actel, ARM) who have provided significant contributions to this research.

Finally, the authors would particularly like to thank Thierry PERRIN and Caroline GARCIA for their significant support.

### Executive Summary

The intent of this report is to provide findings about safety issues when using System on Chip on aircraft and submitting potential approaches for addressing these safety concerns. The scope of the survey has been defined by the call for tender referenced EASA.2008.OP.04 "Safety Implications of the use of system-on-chip (SoC) on commercial of-the-shelf (COTS) devices in airborne critical applications".

The survey has been performed in 4 phases with the participation of:

- The European Aviation Safety Agency (EASA),

- System on Chip providers.

First of all, SoC devices and SoC providers candidates have been selected according to their weight in the aeronautical market and more generally in the electronic market. Moreover, their technical solutions are representative of what can be found on the market today.

Then, during phase 2, the public data related to each candidate device has been analyzed in order to point out potential safety issues and difficulties to meet Certification Specification requirements. This assessment work has been conducted under a structured methodology in order to ensure that all the SoC candidates have been addressed with the same rigor. The methodology consists in assessing the public data against the most popular design assurance alternative methods (reverse engineering, architectural mitigation technique, service history, electronic management plan process...), completed with an assessment against key attributes of the ED80/DO254, deemed pertinent for the SoCs.

On the basis of the phase 2 conclusions, it was clear that it may be necessary to get the support of SoC providers and/or have access to their confidential data to be able to meet design assurance standards. Thus, the possibility to involve SoC providers in a certification process and more generally to get some support from them during the implementation of a SoC has been assessed during the third phase.

To finish, the survey has concluded with the identification of potential amendments to the current hardware certification practices for the use of SoC.

### Background